The combinational logic circuits are a part of digital systems and they have many applications such as decoder, encoder, adder, subtractor, multiplexer and de-multiplexer etc.The basic building block for sequential logic circuits is the flip-flop (FF). Sequential logic circuits are circuits whose outputs at any instant of time depend not only on the present inputs but also on the past outputs.

The basic building block for combinational logic circuits is the logic gate. Combinational logic circuits are circuits in which the output at any time depends upon the combination of the input signals present at that instant only, and does not depend upon any past conditions.Combinational logic circuits and sequential logic circuits. What is the difference between combinational and sequential circuits?ĭigital logic circuits are classified into two groups.

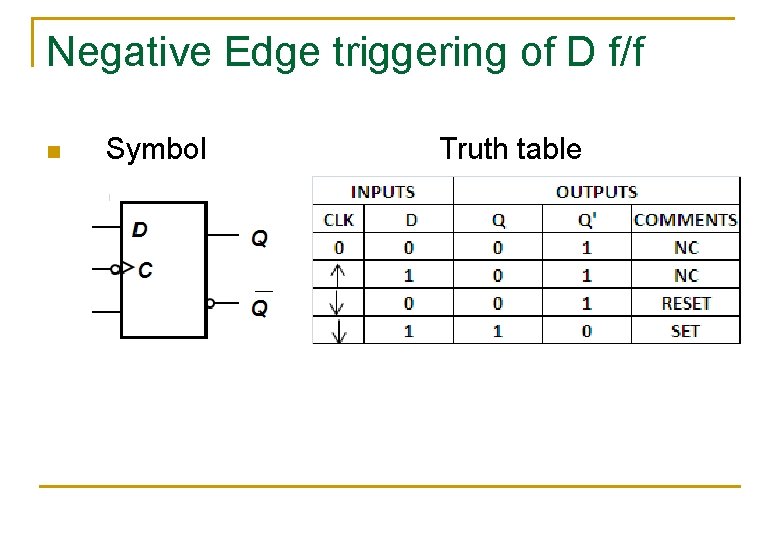

What is the formula used for total propagation delay calculation in asynchronous binary counters?.What is the difference between latches and flip-flops?.What do you mean by the asynchronous inputs of a flip-flop?.Give the difference between positive and negative edge triggering in a flip-flop.What is edge triggered flip-flop and why is it required?.What is the difference between combinational and sequential circuits?.SPI is a good example of a communication protocol that operates this way. That way, there is an entire half clock cycle for the signal to stabilize before it will be read, and slowing down the clock gives more time for outputs to stabilize.

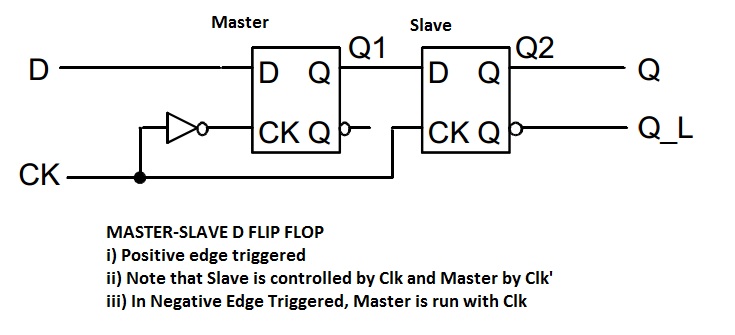

However, for low speed buses routed on PCBs, there is another solution: update outputs on the negative clock edge, and latch inputs on the positive edge. On integrated circuits, FPGAs, and high speed interconnects, this is handled by careful clock routing and detailed knowledge of the setup and hold times of the flip flops, as well as their propagation delay.

Note that this problem is independent of the clock frequency, slowing down the clock doesn't fix it, only fixing the relative delays will help. If the clock has more delay (due to trace length or capacitive loading) than the signal, then the second flip-flop can miss the value. If both flip-flops update on a rising edge, then the second one will be sampling its input at the same time the first is updating the output. This is an issue when you have one flip-flop output driving the input of the next.

0 kommentar(er)

0 kommentar(er)